制造晶体管时使用的另一种结构是增强型 MOSFET (N-channel Metal-Oxide-Semiconductor,N沟道金属氧化物半导体场效应晶体管,缩写为NMOS)。增强型 MOSFET 是一种广泛应用的场效应晶体管。其结构与耗尽型 MOSFET 相同,只是其漏源之间没有内置的沟道。这种器件的电学特性与 JFET 和耗尽型 MOSFET 相似,但显著差异使其在许多应用中非常有趣。

>

>

2N4351 增强型 n 沟道 MOSFET。图片由Linear Systems提供

n 沟道增强型 MOSFET(NMOS)的配置

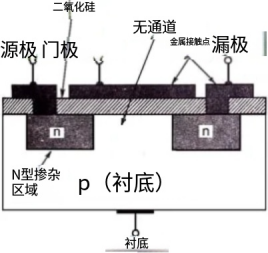

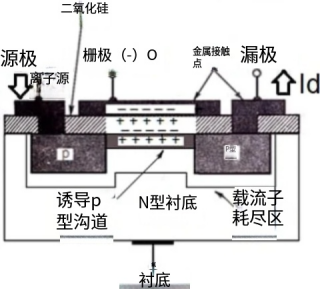

图 1显示了 n 沟道增强型 MOSFET 的结构。

图 1 :n 沟道增强型 MOSFET

p 型衬底为器件提供物理支撑。两个重掺杂的 n 型区构成源极和漏极。源极和漏极区域之间覆盖着一层二氧化硅(SiO2)——一种优异的电绝缘材料。氧化层上方的金属形成栅极电极。源极、漏极和衬底(也称为本体)也有金属接触。

注意源极和漏极之间不存在永久性沟道。

栅源电压 Vgs = 0 的 NMOS 管

通常,p 型衬底和源极会连接在一起。这样,衬底就不会影响器件的工作,MOSFET 将作为一个三端器件工作。

如果栅极也连接到源极,使得栅极和衬底之间没有电势差,那么漏极和源极之间无法流动电流。无论漏极到源极的电压极性如何,总有一个反向偏置的结(二极管)出现在漏极或源极——一个二极管位于 n 型漏极区域和 p 型衬底之间的 p-n 结,另一个二极管位于 p 型衬底和 n 型源极区域之间的 p-n 结。这两个背靠背的二极管阻止了电流流动——这与 JFET 和耗尽型 MOSFET 不同,当 Vgs = 0 时,Id = Idss(饱和短路漏极电流)。

在增强型 MOSFET 中,Idss 的定义没有意义,因为当 Vgs = 0 V 时,Id = 0 A。

由于 n 型掺杂区,在漏极和源极处积累了相当多的自由载流子(电子),如果没有它们之间的路径——漏极和源极之间的路径具有非常高的电阻,这些载流子的积累是无用的。

总之,在栅极不加电压的情况下,晶体管在漏极和源极之间相当于开路。

NMOS 管栅源电压 Vgs > 0

栅极施加的电压调节了源极和漏极之间的电流流动。

给栅极电压 Vgs 一个较小的正值,栅极上的正电荷会排斥栅极下衬底中的自由空穴,使它们进入 p 型衬底的更深处,并在源极和漏极之间的 SiO2绝缘层附近形成一个载流子耗尽区。

与受主原子相关的束缚负电荷占据了载流子耗尽区。这些电荷之所以“暴露”出来,是因为中和空穴被驱入了衬底。

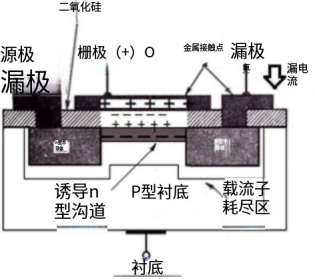

使栅极更正,栅极上的电荷将自由电子从 n 型源区和漏区(那里有很多)吸引到载流子耗尽区。积累的电子在氧化硅界面诱导出 n 型沟道,连接漏极和源极,如图 2所示。

图 2: 增强型 NMOS 的沟道形成

现在电流可以流过晶体管,在漏极和源极之间施加电压。该电流将通过感应形成的 n 型区域从漏极流向源极,由自由电子携带。

诱导沟道的另一个名称是反型层——因为它是由将衬底表面从 p 型转换为 n 型而形成的。

图 2还显示了栅极和沟道之间形成的平行板电容器——其中 SiO2绝缘层作为电介质——由正 Vgs 引起的正电荷在顶板上积累,以及由沟道中的电子产生的结果负电荷。

NMOS 是一种场效应晶体管(FET)。因此,在电容中会形成电场,以控制沟道中的电荷数量、其导电性和流过电流的大小。

阈值电压 VT是指沟道形成时的 Vgs 电压。阈值电压的大小取决于衬底的电学特性和氧化层特性及厚度。对于 NMOS,VT为正值。

器件的制造工艺控制 VT的值,并在规格书中显示为 Vgs(Th)。

当栅极电压低于阈值电压时,电流 Id = 0 A,因为在这种情况下不存在沟道。

将栅极电压升高至 VT以上会在沟道中感应更多自由电子,从而降低其电阻。此时,器件相当于一个电压控制电阻。当沟道被夹断时,MOSFET 相当于一个电压控制恒流器件。

NMOS 在栅源电压 Vgs < 0 时

耗尽型 NMOS 或 JFET 的栅极电压可以根据 Vgs 是负还是正来耗尽或增强沟道中自由载流子的浓度。增强型 NMOS 的栅极电压只能增强沟道中自由载流子的浓度——该晶体管仅在增强模式(Vgs > 0)下工作。这个条件是命名该器件为增强型 MOSFET 的基础。

在漏极和源极之间施加电压

维持感应沟道所需的最低电压是阈值电压 VT。形成感应沟道并将漏极相对于源极设为正,会导致电流 Id 的流动。自由电子从源极流向漏极,电流 Id 的方向从漏极到源极,如图 2 所示。由于输入阻抗很高,栅极电流 Ig = 0 A。

漏源电压较小时,沟道不会发生 pinch-off,此时 NMOS 像一个线性电阻,其阻值由 Vgs 控制。

增加漏源电压会像耗尽型 NMOS 和 JFET 一样,在沟道漏极处触发 pinch-off。

pinch-off 在沟道漏极处开始形成,当

Vgd = VT> 0 (1)

但是 Vgd = Vgs – Vds (2),则

Vgs – Vds = VT> 0 (3),或

Vds = Vgs – VT> 0 (4).

当 Vds 小于公式 4中的值时,沟道不会夹断。

保持 Vgs 恒定并增加 Vds,漏极电流最终会达到饱和水平。例如,将方程 2 中的 Vgs 固定在某个值,比如 8V,并将 Vds 从 2V 增加到 5V,Vgd 会从 6V 减少到 3V。这意味着栅极相对于漏极的电位变得更低。

这个栅极到漏极电压的降低会减弱这个感应沟道区域中自由载流子——电子——的吸引力,并减小有效沟道宽度。最终,增加 Vds 会使沟道收缩到夹断点,建立饱和条件——NMOS 进入饱和区或饱和模式。

当 Vds 超过 pinch-off 值时,沟道上的电压降保持在公式 4的 Vds 值,恒定不变。无论 Vds 的大小如何,漏极电流 Id 也保持恒定(处于饱和水平)。因此,在饱和状态下,沟道上的电压降和通过它的电流都保持不变。

沟道 pinch-off 并不意味着沟道阻塞——电流仍然通过被 pinch-off 的沟道继续流动。

NMOS 的漏极特性曲线和传输特性曲线

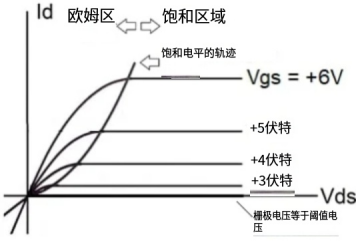

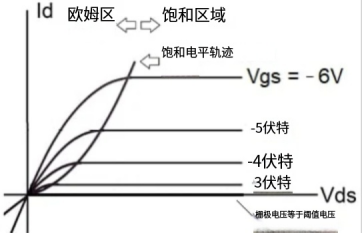

图 3展示了一个增强型 NMOS 的漏极特性曲线示例。增强型 NMOS 的伏安特性曲线与 FET 特性曲线具有相同的形式。

图 3 :增强型 NMOS 的漏极特性

注意,当 Vgs ≤ VT时,欧姆区的电阻为无穷大,随着 Vgs 的增加而减小。虽然 Vgs 是图 3中特性的参数,但它们取决于 Vgs - VT——有效电压或过驱动电压。

公式 4展示了 Vds 饱和程度与 Vgs 幅值之间的关系。对于固定的 VT值,Vgs 越高,导致饱和的 Vds 值就越大。

图 3表明,漏极特性的饱和部分是一条水平直线。随着 Vgs 的上升,Id 的饱和程度增加,从 VT值开始到+ 6 V。注意,随着电压的增加,Vgs 各级之间的间距增大,导致漏极电流的增量增大。增强型 NMOS 的漏极电流 Id 在 Vgs < VT时为 0 A。

将漏极特性扩展到足够高的漏极电压会引发沟道击穿。这种失效是由沟道漏极侧耗尽区的雪崩击穿引起的。

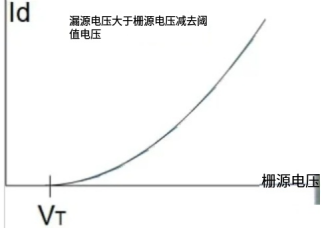

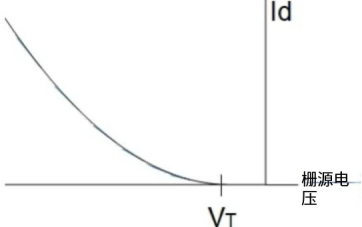

图 4显示了增强型 NMOS 的传输特性。

图 4:增强型 NMOS 的传输曲线

当 Vgs > VT时,Id 和 Vgs 通过非线性关系相关

Id = k(Vgs - VT)² (5)

其中常数 k 取决于器件的物理特性。

增强型 NMOS 的传输特性曲线完全位于正 Vgs 区域,并在 Vgs = VT时开始上升。

传输特性曲线遵循漏极特性的饱和水平。因此,工作区域是 Vds 值大于由公式 4定义的饱和水平的区域。

P 沟道耗尽型 MOSFET(PMOS)的配置

增强型 PMOS 与 NMOS 相反,如图5所示。它具有 n 型衬底,在漏极和源极连接处有 p 型区域。识别端子的方式与 NMOS 相同,但电压极性和电流方向相反。NMOS 和 PMOS 是互补型晶体管。

图 5:增强型 PMOS 中的沟道形成

在栅极和源极之间施加负电压会诱导一个 p 型沟道——带有 p 型载流子——允许电流在源极和漏极之间流动。电场垂直穿过氧化层,在半导体侧的诱导正电荷处结束。正电荷——n 型衬底中的少数电荷——形成反型层。

PMOS 的漏极特性和传输特性

图 6显示了增强型 PMOS 的漏极特性。

图 6:增强型 PMOS 的漏极特性

增加栅源负电压的幅度会提高半导体中感应的正电荷以及氧化层下区域的导电性。因此,负栅极电压增强了漏极电流 Id。

图 6显示,电流 Id 起初缓慢上升,然后随着 Vgs 越来越负而迅速增加。

图 7显示了增强型 PMOS 的传输特性曲线。

图 7:增强型 PMOS 的传输特性曲线

这条传输特性曲线是图 4传输特性曲线的镜像,随着 Vgs 超过 VT 而越来越负,Id 会持续增加。

增强型 MOSFET 总结

- 增强型 MOSFET 具有小尺寸、低功耗和易于制造的特点。这些特点使它们适合用于集成电路。

- 当在栅极和源极端子之间未施加电压时,漏极和源极之间没有通路。

- 施加栅极-源极电压可以增强沟道,使其能够导通电流。这一特性是将其标记为增强型 MOSFET 的原因。

- 增强型 MOSFET 仅工作在增强模式,而耗尽型 MOSFET 则可以在增强和耗尽模式中工作。

- 对 NMOS 施加正的栅源电压会形成 n 型沟道层,允许自由载流子从源极到漏极导通。

- 阈值电压 VT是开始形成漏源沟道的栅源电压。当 Vgs 小于 VT时,漏源沟道不存在,漏极电流 Id = 0 A。

- 阈值电压 VT的大小取决于器件的结构特性,每个 MOSFET 都有特定的值。

- JFET 和耗尽型 MOSFET 中找到的 Idss 量不适用于增强型 MOSFET,因为当 Vgs = 0 V 时,Id = 0 A。

- 在增强型 PMOS 中,负的 Vgs 会形成一个 p 型通道层,该通道层从源极到漏极传输自由载流子。